Ver traducción automática

Esta es una traducción automática. Para ver el texto original en inglés haga clic aquí

#Energía

{{{sourceTextContent.title}}}

El módulo del FET de GaN del Mitad-Puente viene en QFN

{{{sourceTextContent.subTitle}}}

Un QFN contiene 80 V, 10 una etapa de la energía del mitad-puente del FET de GaN y su conductor asociado de la puerta.

{{{sourceTextContent.description}}}

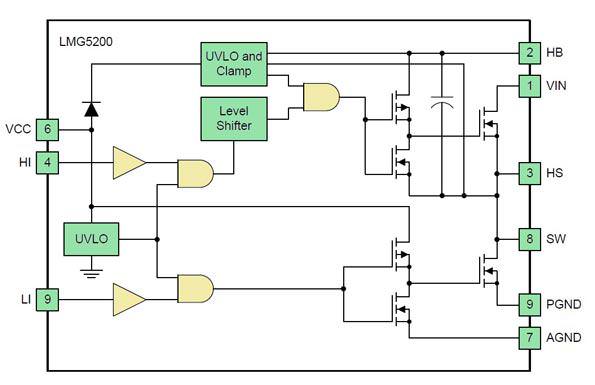

Texas Instruments ha embalado dos FETs de GaN y un conductor de alta frecuencia de la puerta en una configuración del mitad-puente que produce 80 V, 10 A. La etapa de la energía LMG5200 (la fig. tecnología de envasado avanzada del multichip de las características de 1) y se optimiza para apoyar las topologías de la conversión de energía que funcionan en las frecuencias hasta 5 megaciclos. Las entradas LMG5200 son TTL-compatibles, y pueden soportar hasta 14 V sin importar VCC. El cuadro 1 describe las conexiones de perno LMG5200.

El LMG5200 es una etapa completa, confiable de la energía, consistiendo en un conductor y un FET optimizados funcionamiento de GaN de la energía. Todos los dispositivos se montan en una plataforma totalmente enlazar-alambre-libre del paquete con los elementos parásitos reducidos al mínimo del paquete. Las consideraciones especiales durante diseño de paquete se aseguran de que la inductancia de la fuente común, la inductancia del lazo de la puerta y la inductancia del lazo de la energía estén reducidas perceptiblemente.

¿Esta etapa de la energía de GaN del mitad-puente integra dos, 18 m? Los FETs de GaN con el alto-lado y el bajo-lado bloquean conductores. Incluyendo la puerta el conductor en el módulo mejora eficacia de la energía-etapa reduciendo inductancias parásitas en el crítico puerta-conduce el lazo. También, los retardos de propagación entre el alto-lado y los conductores de la puerta del bajo-lado se emparejan para permitir control muy apretado del tiempo muerto. Para mantener eficacia alta, el tiempo muerto que controla es crítico en usos GaN-basados. Usted puede controlar independientemente entradas del HI y de LI para reducir al mínimo la tercera conducción del cuadrante del FET del bajo-lado para los convertidores difícilmente cambiados del dólar. Una unión mal hecha muy pequeña de la propagación entre el HI y el LI a los conductores para los umbrales que caen y de levantamientos permite épocas muertas en la gama de 10 ns. el Co-empaquetado del mitad-puente del FET de GaN con el conductor de la puerta reduce al mínimo la inductancia de la fuente común esa las topologías difícilmente cambiadas de los impactos.

Un circuito del elástico de bota con la abrazadera previene la impulsión de la puerta del alto-lado de exceder el voltaje máximo de la puerta-a-fuente de los FETs de GaN (VGS) sin ninguÌn trazado de circuito externo adicional. El conductor de la puerta tiene un cierre del undervoltage (UVLO) en el VCC y los carriles del elástico de bota (HB-HS). Cuando el voltaje está debajo del voltaje del umbral de UVLO, el dispositivo no hace caso de las señales del HI y de LI de evitar que los FETs de GaN sean girados parcialmente. Debajo de UVLO, si hay el suficiente voltaje (VCC > 2.5 V), el conductor tira activamente del conductor del alto-lado y de la puerta del bajo-lado hecho salir punto bajo. La histéresis del umbral de UVLO de 200 milivoltio evita el rechino y el excitamiento indeseado debido a los puntos de voltaje.

¿Para simplificar la fabricación, el LMG5200? s 6 milímetros por 8 el paquete del milímetro QFN no requiere ninguÌn underfill, usado a veces para resolver requirments de la avería del contorneamiento. El más, su huella reducida aumenta la adopción de los diseños de la energía de GaN en una gama de usos amplia, de la nueva carga sin hilos de alta frecuencia a la telecomunicación de 48 V y a los diseños industriales.

Debido al parasitics que puede ocurrir durante la disposición del empaquetado y de diseño, los diseños GaN-basados de la energía han tenido incertidumbres asociadas a sus circuitos del conductor. Por lo tanto, los diseñadores que utilizan los altos FETs de GaN de la frecuencia de la conmutación deben ejercitar cuidado con la disposición del tablero para evitar sonar y EMI. La disposición apropiada de los componentes externos usados con el LMG5200 es crítica a alcanzar del funcionamiento deseado. También, la disposición de los condensadores para proporcionar el de alta frecuencia que desempareja para los casquillos de la entrada del conductor y del elástico de bota de la puerta es crítica asegurarse de que no hay pérdida de impulsión de la puerta durante la conmutación de alto voltaje y la conmutación actual.

Para prevenir las faltas catastróficas debido al recalentamiento, es crítico que el tablero de p.c. exhibe resistencia termal baja con el LMG5200 en la temperatura ambiente bajo condiciones de funcionamiento del peor caso. Siguiendo las pautas para un diseño de múltiples capas del tablero (http://www.ti.com/lit/an/snva729/snva729) usted obtendrá la ventaja máxima de un módulo integrado del mitad-puente del conductor de la puerta y del FET de GaN termalmente y eléctricamente.

Para maximizar las ventajas de la eficacia de la conmutación rápida, es extremadamente importante optimizar la disposición del tablero para la impedancia mínima del lazo de la energía. Al usar a un tablero con más de dos capas usted puede reducir al mínimo impedancia parásita del lazo de la energía teniendo la trayectoria de vuelta al condensador de la entrada (entre VIN y PGND) pequeño y directamente por debajo la primera capa. La inductancia del lazo es reducido debido a la cancelación de la inductancia pues la corriente de vuelta está directamente debajo y fluyendo en la dirección opuesta. Es también crítico que los condensadores VCC y los condensadores del elástico de bota están tan cerca al dispositivo como posible y en la primera capa. La conexión de AGND del LMG5200 no se debe conectar directamente con PGND de modo que el ruido de PGND no cambie de puesto directamente AGND y no cause los acontecimientos falsos de la conmutación debido al ruido inyectado en señales del HI y de LI. Utilice el espaciamiento apropiado en la disposición para reducir contorneamiento y para mantener requisitos de separación de acuerdo con el nivel de la contaminación del uso.

¿Fig. 2 identifica el impacto del parasitics del nivel de tablero en el funcionamiento de LMG5200? lazos dominantes de s. La inductancia del lazo del poder más elevado (demostrada en rojo) causa overshoot significativo en el nodo del interruptor. El overshoot causa una pérdida de eficacia debido a las pérdidas que cambian crecientes. Para reducir al mínimo esta inductancia del lazo, es crítico utilizar las técnicas de la disposición que eliminan con eficacia la inductancia parásita del lazo.

La adición de capacitancia parásita del nodo del interruptor es también un mecanismo de la pérdida de la conmutación pues el condensador parásito se carga y se descarga al voltaje del nodo del interruptor con cada ciclo de la conmutación. Reduzca al mínimo la capacitancia del interruptor-nodo reduciendo el traslapo entre el plano del interruptor-nodo y la tierra y los planos de VIN. Para reducir al mínimo la capacitancia agregada del nodo del interruptor, se recomienda que haya un recorte para el nodo del interruptor en el plano del metal 2 y posiblemente las capas subsecuentes también. Además, el control sensible y las señales analógicas se deben guardar lejos del perno del interruptor y de la red del interruptor-nodo para reducir al mínimo el acoplador e interferencia. Localice el inductor de la energía tan cerca al IC como sea posible reducir al mínimo el área del interruptor-nodo, reduciendo capacitancia y la EMI parásitas.

Para eliminar la pérdida falsa de energía de entrada, reduzca al mínimo la inductancia parásita de la entrada que desempareja los condensadores a VCC y a AGND. Semejantemente, prevenir apagón en el conductor del alto-lado y causar cierre del undervoltage, reducir al mínimo la inductancia agregada entre el condensador del elástico de bota y el HB-HS eligiendo un condensador apropiado y técnicas sugeridas de la disposición.

Puente apropiado de la fuente del bajo-lado y de los conductores del alto-lado es esencial en el abastecimiento de funcionamiento estable de la conmutación sin el malfuncionamiento. Usando 0402 clasificó los condensadores, colocados inmediatamente adyacente al IC en la capa superior reduce al mínimo que la inductancia del rastro para el condensador del elástico de bota a HS-HB.

Elija un condensador 0402 para que VCC el desemparejamiento reduzca al mínimo la inductancia del rastro del condensador al VCC, pernos de AGND. La inductancia excesiva en estos lazos puede causar una pérdida de impulsión de la puerta al alto-lado y al bajo-lado, que lastimarán funcionamiento de la eficacia y del circuito. Si la inductancia es alta entonces una pérdida falsa de la señal de impulsión debajo del umbral del cierre del undervoltage hará el dispositivo apagar la fuente de la puerta totalmente para prevenir daño a los FETs de GaN.

Además de obtener el módulo de la evaluación LMG5200 (EVM), los diseñadores pueden conseguir comenzados más rápidamente a usar PSpice

{{medias[4352].description}}